CIESコンソーシアム

産学共同研究

スピントロニクス LSI技術

不揮発記憶ベース低消費電力・高性能VLSI プロセッサの自動設計環境の研究開発

-

研究代表者

研究代表者

羽生 貴弘 教授

4x世代以降における深刻な待機電力の増大に起因した性能限界を突破するため、不揮発ベース低消費電力・高性能回路IPの設計開発、およびそれらを活用した自動設計環境を構築することが本テーマの課題であり、主に以下の研究に取り組んでいます。

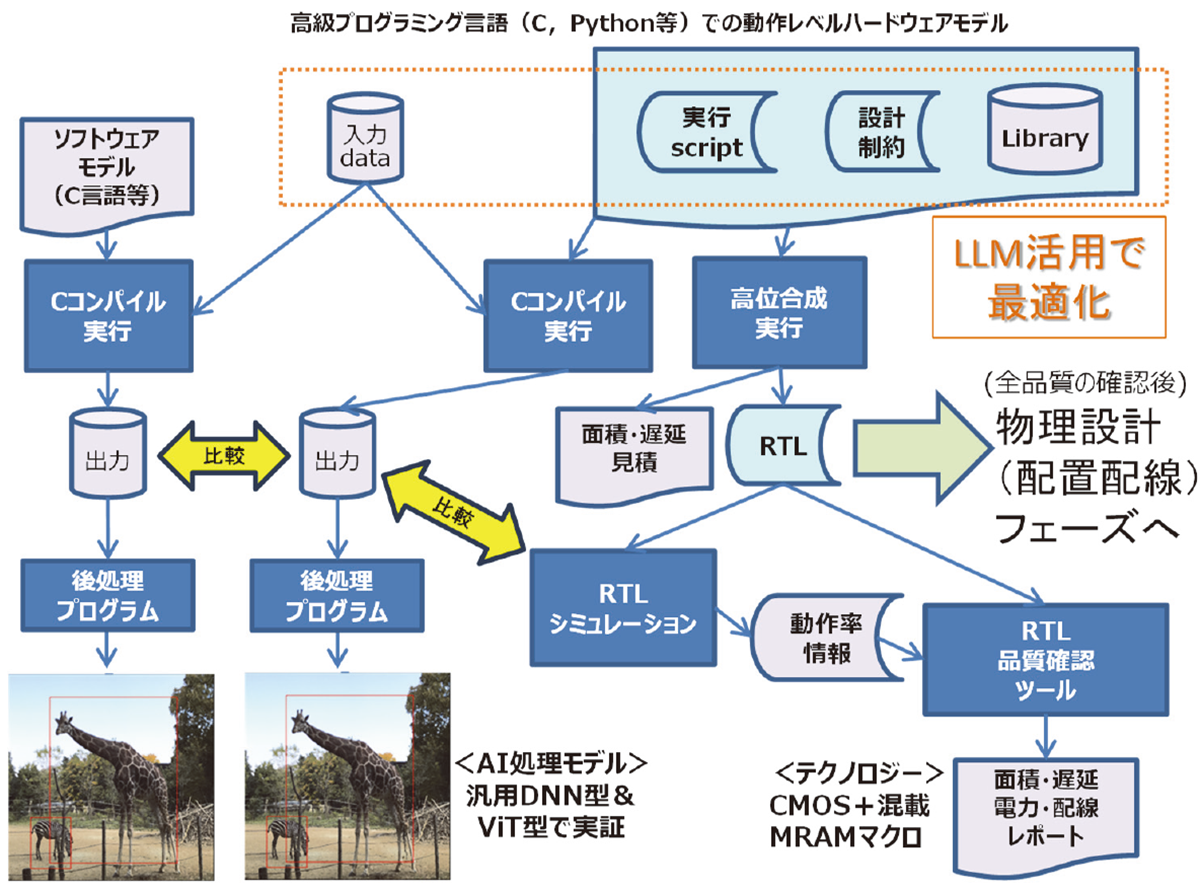

- 自動設計CAD環境の構築(図参照)

MRAMなど新規バックエンドメモリを搭載した不揮発ベース低消費電力・高性能回路・システムの自動設計CAD環境構築を行っています。 - 不揮発ベース回路IP群のさらなる改良

不揮発FPGAのさらなる高性能化・多機能化に向け、その基本構成回路IP(LUT (Lookup Table) 回路や不揮発レジスタ等)の開発も行っています。 - AIアクセラレータ等への応用

不揮発ベース回路・システムの具体的応用例として、超低消費電力AIアクセラレータの開発にも取り組んでいます。

上述した技術によりVLSIプロセッサの電力効率が高まることで、モバイル機器やIoT機器などへの積極的応用が期待されます。